简 介

混合信号系统设计研究方向含高性能混合信号集成电路的设计理论与技术(高性能转换器架构研究、混合信号电路的数字校准技术研究)、模-数/数-模转换器(ADC/DAC)电路设计、电源管理芯片、PLL电路设计等子方向。

以重大装备研制需求为牵引,开展数模混合信号集成电路设计理论与技术的研究,以及数据转换器集成电路关键元器件的设计。根据国际上模拟元器件包括数据转换技术与系统的发展趋势开展高速度、高精度数模、模数转换技术的研究工作。“十一五”“十二五”期间承研部委预研项目、预研基金项目、新品研制项目以及国家自然科学基金面上项目等多项科研项目。

成果简介

专项技术1:数据转换器后台全数字校准

技术特征:

旨在研究高性能转换器的快速收敛数字校准技术,从而突破集成电路工艺按比例缩小和系统集成的限制,利用大规模数字电路在工艺、面积和功耗上的优势,减轻高性能转换器存在于架构、工艺、性能、面积、功耗等多方面的设计约束。

研究DAC的动态元匹配DEM技术、时间交叉ADC通道间误差校准技术以及基于伪随机噪声注入的单通道ADC实时后台数字校准技术、双通道互校准技术研究,设计采用单通道PN注入校准、Split校准、双转换校准等主流校准技术的转换器后台数字校准电路IP核。

应用前景:

14位以上高速转换器,包括Pipeline架构及SAR架构ADC转换器,电流源型DAC

前期投入:

国家自然科学基金面上项目,2010.1--2013.12

部委预研项目,2011,1--2015.12

技术状态:

完成研发,完成样片流片及封装测试。

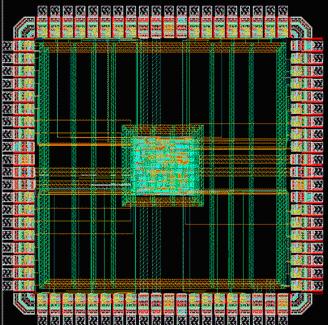

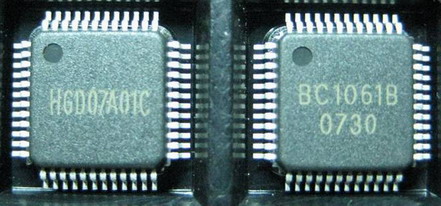

数字校准技术IP核

数字校准技术IP核测试样片

专项技术2:高速高位A/D转换器

技术特征:14位125MSPS ADC,12位200MSPS ADC

应用前景:无线通信、雷达、仪器仪表

技术状态:

14位ADC完成测试样片流片及测试;12位ADC在研发后期,完成设计,在开发版图。

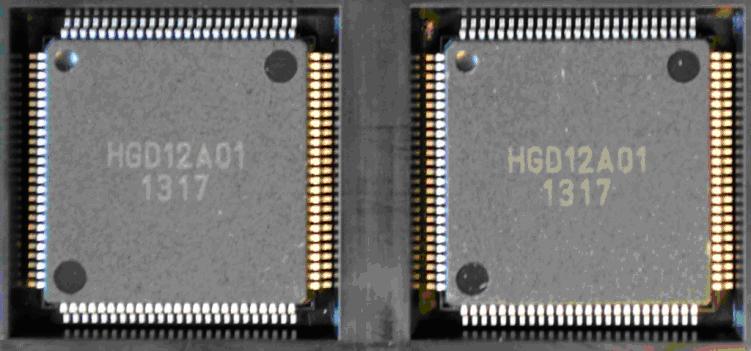

14位高速A/D转换器

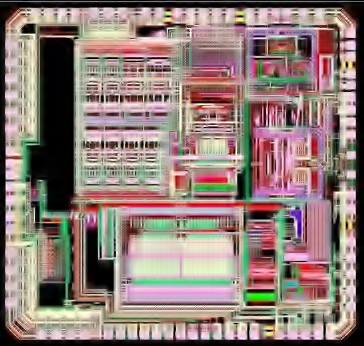

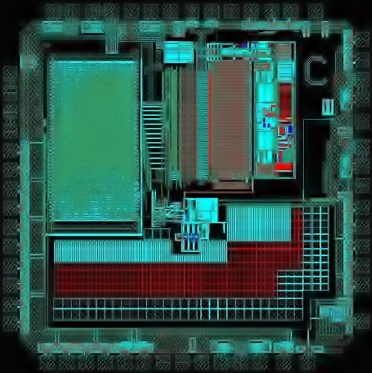

14位A/D转换器版图

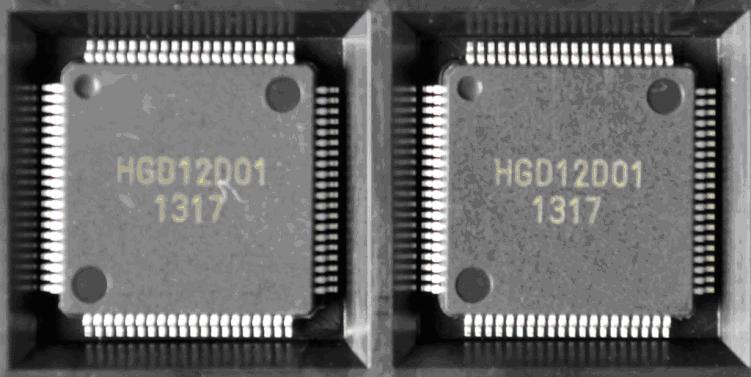

14位A/D转换器样片

专项技术3:高速高位D/A转换器

技术特征:14位130MSPS DAC(内核转换300M),12位400MSPS DAC

应用前景:无线通信、雷达、仪器仪表

前期投入:部委预研项目,新品项目,2006.1--2010.12

技术状态:

14位DAC完成流片、测试;12位DAC在研发后期,完成设计,在开发版图。

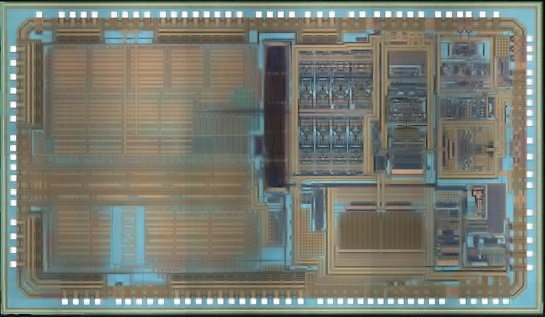

14位D/A转换器版图

14位高速D/A转换器

专项技术4:高位ADC转换器设计

技术特征:24位delta-sigma ADC

应用前景:衡具、压力传感器、工业控制

技术状态:设计开发中

专项技术5:其他

[1] 算术协处理器芯片MD80C287A:1.5μm CMOS工艺,通过流片、测试,已用上装备;

[2] 低功耗容栅传感测量专用集成电路芯片:流片,已用于数字式游标卡尺;

[3] CMOS锁相环时钟发生器:0.25μm MS CMOS工艺,完成流片、测试;

[4] 10位逐次逼近型低功耗A/D转换器:0.25μm CMOS工艺,完成设计;

[5] LDO线性整流器:支持辅助备用电源,500毫安,3.3V,0.5um CMOS工艺,完成设计。

近5年来发表的主要文章

2012年度:

[1] Yong-sheng Yin, Rui Zhang, Jun Yang, Ming-lun Gao. Calibration Method Considering Second-Order Error Term of Timing Skew for A Novel Multi-Channel ADC, Proceedings 2011 9th IEEE International Conference on ASIC, Xiamen, pp1020-1023, 2011.10.25. ( EI20122015028878 )

[2] Zhang Rui, Yin Yongsheng, Gao Minglun. SPLIT-ADC BASED DIGITAL BACKGROUND CALIBRATION FOR TIME-INTERLEAVED ADC, 电子科学学刊(英文版), 2012, 29(3): 302-309.

[3] Wang Liang*, Yin Yong-Sheng*, Guan Xian-Zhong. Design of a gain-boosted telescopic fully differential amplifier with CMFB circuit, 2012 2nd International Conference on Consumer Electronics, Communications and Networks, Yichang, p252-255, 2012.04.21-23. (EI20122415104117)

[4] Xian-zhong Guan,Hong-hui Deng,Liang Chang. Opamp-sharing MDAC Design for Pipelined Successive-Stage of a1.8V80MS/s 14-bit Pipelined ADC, 2012IEEE International Conference on Anti-Counterfeiting,Security and Identification, pp140-143, Taipei, 2012.08.24-25. (EI20125015782841)

[5] Lei Quan, Yongsheng Yin*, Xinbo Yang, Honghui Deng. Design of a High Precision Band-gap Reference with Piecewise-Linear Compensation, 2012 IEEE International Conference on Anti-Counterfeiting, Security and Identification, pp275-279, Taipei, 2012.08.24-25. (EI20125015782871)

[6] Mingwen Zhang, Yongsheng Yin*, Honghui Deng, Hongmei Chen. Design of Low-jitter Clock Duty Cycle Stabilizer in High-performance Pipelined ADC, 2012 IEEE International Conference on Anti-Counterfeiting, Security and Identification, pp148-152, Taipei, 2012.08.24-25. (EI20125015782843)

[7] Xinbo Yang, Honghui Deng, Lei Quan, Yongsheng Yin. A differential reference voltage source and its output buffer used in high-speed high-precision pipelined ADC. 2012 5th International Congress on Image and Signal Processing, Chongqing, p1652-1656, 2012.10.16-18. (EI待检索)

[8] Ming Wang, Yongsheng Yin, Rui Zhang, Wei Lin, Wei Ni. An Extensible FPGA-based Postprocessor Architecture of Timing Skew Correction for Time-Interleaved ADCs, 2012 5th International Congress on Image and Signal Processing, Chongqing, pp1696-1699, 2012.10.16-18. (EI待检索)

[9] Yi-Long Zhu, Yong-Sheng Yin, Ming Wang, Wei Ni. A Research on Digital Background Calibration Algurithm for Pipelined ADC and the Implementation of Full FPGA Verification Platform, 2012 5th International Congress on Image and Signal Processing, Chongqing, p1683-1686, 2012.10.16-18. (EI待检索)

[10] 张睿, 尹勇生. 流水线模数转换器设计, 电子测量与仪器学报, 2012, 26( 3):223-228.

[11] Xiao-lei Wang, Chang Liang, Xian-zhong Guan, Hong-hui Deng. A 2.5bit SMDAC With Op-sharing Technique Between S/H And First MDAC. 2015 5th International Congress on Image and Signal Processing, Chongqing, p1648-1651, 2012.10.16-18. (EI待检索)

2011年度:

[12]Yong-sheng Yin, Rui Zhang, Jun Yang, Ming-lun Gao. Calibration Method Considering Second-Order Error Term of Timing Skew for A Novel Multi-Channel ADC. Proceedings 2011 9th IEEE International Conference on ASIC, Xiamen, pp1020-1023, 2011.11.25. (EI20122015028878)

[13] Rui ZHANG, Yong-sheng YIN*, Jun YANG, Ming-lun GAO. Dual-ADC based Digital Calibration of Timing Skew for a Time-Interleaved ADC, Proceedings of the International Conference on Image Analysis and Signal Processing, Wuhan, pp42-45, 2011.10.21. (EI20120414709663)

[14] Ye Wang, Yong-Sheng Yin, Liang Wang, Hong-Hui Deng. Design of the high-speed high-resolution Latched comparator, 2011 IEEE 3rd International Conference on Signal Processing Systems, Yantai, p597-600, 2011.08.27. (EI待检索)

[15] Peng Huang, Hong-hui Deng, Yong-sheng Yin. A High Performance 50% Clock Duty Cycle Regulator. Intelligent Computing and Information Science(2011), pp208-214. (EI待检索)

[16] Chong Duan, Hong-Hui Deng,Rui Zhang,Yong-Sheng Yin. A 1.2V High Performance Operational Transconductance Amplifier, 2011IEEE 3rd International Conference on Signal Processing Systems(Vol.1), Yantai, pp605-608, 2011.08.27. (EI待检索)

[17] Jun Yang, Hong-Hui Deng, Rui Zhang,Y ong-Sheng Yin. A 100-MS/s CMOS Sample-and-Hold Circuit with input common mode feedback, 2011IEEE 3rd International Conference on Signal Processing Systems(Vol.2), Yantai, pp173-176, 2011.08.27. (EI待检索)

[18] Zheng Dan, Ni Wei, Zhang Rui, Yin Yongsheng. An Improved Data Weighted Averaging for Segmented Current-Steering DACs. 2011IEEE 3rd International Conference on Signal Processing Systems(Vol.2), Yantai, pp177-181, 2011.08.27. (EI待检索)

[19] 陈红梅,邓红辉,张明文,陶阳,尹勇生. 高速低抖动时钟稳定电路设计, 电子测量与仪器学报, 2011, 25( 11):223-228.

2010年度:

[20] Fei Pei, Honghui Deng, Yongsheng Yin. Design of Power Scaleable MDAC in High Performance Pipelined ADC. Proceedings 2010 International Conference on Anti-Counterfeiting,Security and Identification, Chengdu, pp126-129, 2010.07.18. (EI20104113279174)

[21] Rui Zhang*, Yong-Sheng Yin, Shang-Quan Liang, Ming-Lun Gao. A Multi-bit Multiplying Digital-to-Analog Converter With Bi-directional overflow detection. 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology Proceedings, Shanghai, pp427-429, 2010.11.01. (EI20110413609614)

[22] LIANG Shang-Quan*, YIN Yong-Sheng, DENG Hong-Hui, ZHANG Rui, HU Jun. A Research on the Fast Correlation-Based Background Calibration Techniques for the Pipeline ADCs, 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology Proceedings, Shanghai, pp430-432, 2010.11.01.

(EI20110413609610)

[23]Rui Zhang, Hong-Hui Deng, Yong-Sheng Yin, Shang-Quan Liang,Ming-Lun Gao. A High-Performance Sample-and-Hold Circuit for 14-bit 125MS/s Pipelined ADC. 2010 10th IEEEInternational Conference on Solid-State and Integrated Circuit Techmology Proceedings, Shanghai, pp424-426, 2010.11.01. (EI20110413609613)

[24] Jun Hu, Yongsheng Yin*, Honghui Deng. Design of a High-performance Brokaw Band-gap Reference, Proceedings 2010 International Conference on Anti-Counterfeiting, Security and Identification, Chengdu, pp126-129, 2010.07.18. (EI20104113279170)

[25] Shuming Yang, Yongsheng Yin*, Honghui Deng. Design og An Outer-chip Controllable and Inner-chip Adjustable Voltage Reference, Proceedings 2010 International Conference on Anti-Counterfeiting, Security and Identification, Chengdu, pp134-137, 2010.07.18. (EI20104113279168).

[26] Guan Haowei*, Yin Yongsheng*, Deng Honghui*. Integrated Digital Control Pulse Generator, 2010 2nd IEEE International Conference on Information Management and Engineering, Chengdu, pp387-390, 2010.04.16.(EI20102913087022)

[27] Zhang Guo-min*, Yin Yong-sheng*, Deng Hong-hui*, MDAC Design for 1.5-bit Pipeline Stage of High-Speed High-Resolution ADC, The 2nd International Conference on Advanced Computer Control, Shenyang, pp456-459, 2010.03.27. (EI20104213306237).

2009年度:

[28] LIANG Shang-Quan*, YIN Yong-Sheng, DENG Hong-Hui, WANG Xiao-Lei, GAO Ming-Lun. A Mixed-Signal Calibration Techology for the Pipeline A/D Converter. Proceedings 2009 8th IEEE International Conference on ASIC, Changsha, pp242-245, 2009.10.20. (EI 20101112773116)

[29] Honghui Deng, Yongsheng Yin, Gaomin Du. Phase Noise Analysis and Design of CMOS Differential Ring VCO. 2009 9th International Conference on Electronic Measurement & Instruments, Beijing, pp731-736, 2009.08.16.(EI20095112549608)

[30] Qin Su, Yongsheng yin, Honghui Deng. Design of a low Voleage High Precision CMOS Bandgap Reference. 2009 9th International Conference on Electronic Measurement & Instruments, Beijing, pp342-345, 2009.08.16.(EI20095112549485)

[31] Deng Liang 、Deng Hong-hui 、Yin Yong-sheng、Zhang Guo-min. 1-V rail-to-rail constant-tranconductance operation amplifier. 2009 9th International Conference on Electronic Measurement & Instruments, Beijing, pp798-801, 2009.08.16.(EI20095112549361)

软硬件环境

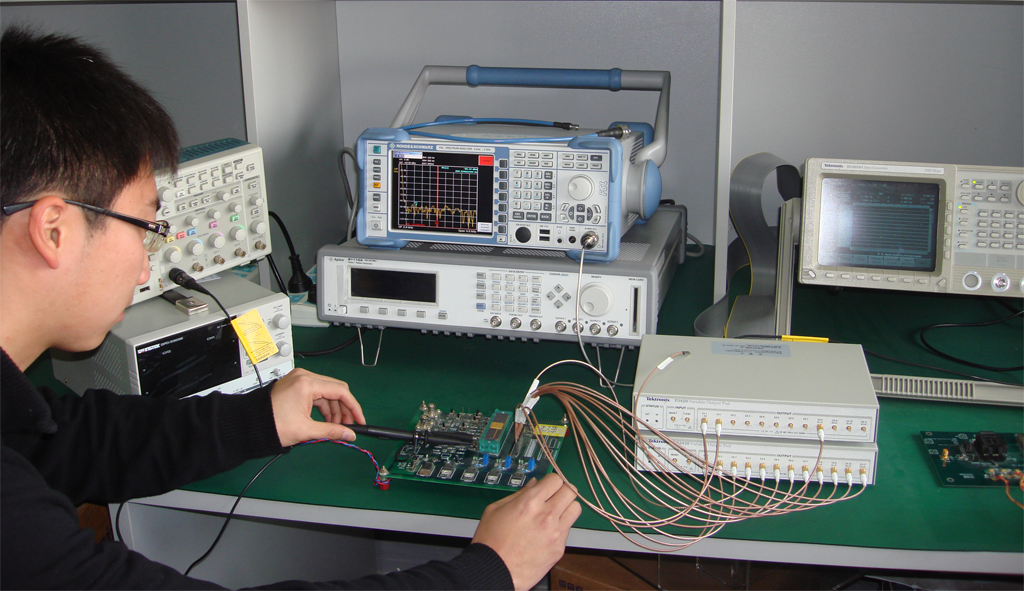

混合信号集成电路设计研究室拥有全套Cadence EDA工具软件包(大学计划)以及Mentor和其他相关EDA软件;SUN服务器M3000 1台,工作站以及PC 20多台;多套XILINX、ALTERA公司的FPGA开发系统;逻辑分析仪(TLA5202)、频谱分析仪(FSL3)、数字任意波形发生器(DG2020A)等多台测试仪器,以及完整的混合信号系统原型实验平台及测试平台。

混合信号系统原型实验平台

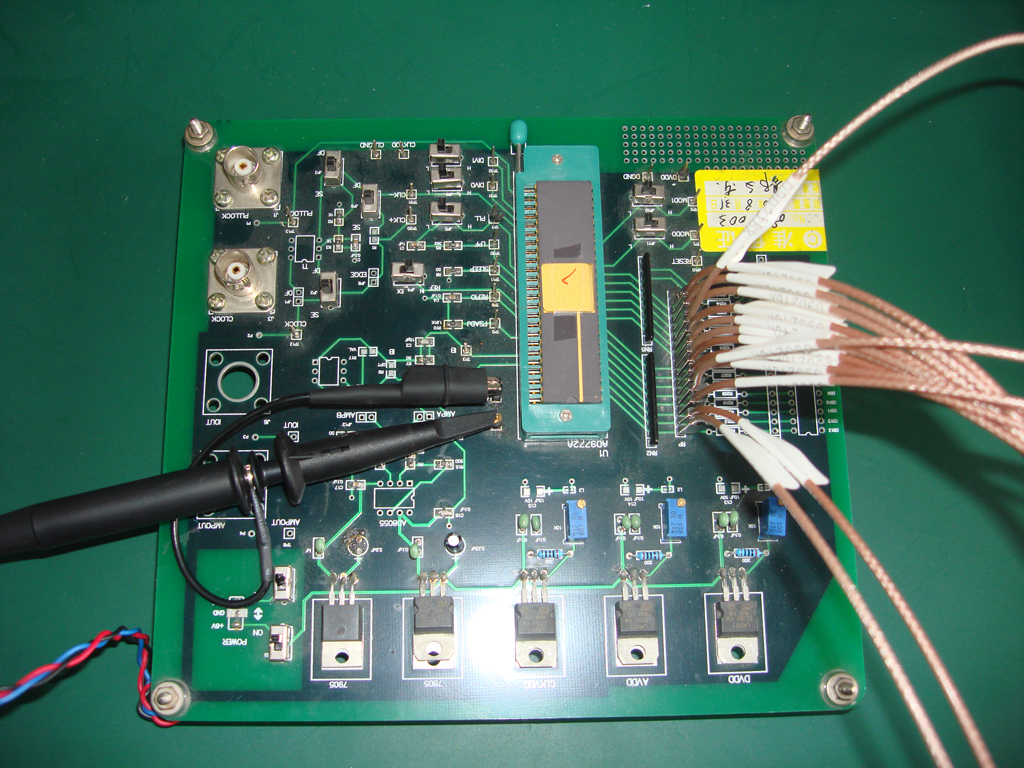

样片测试板

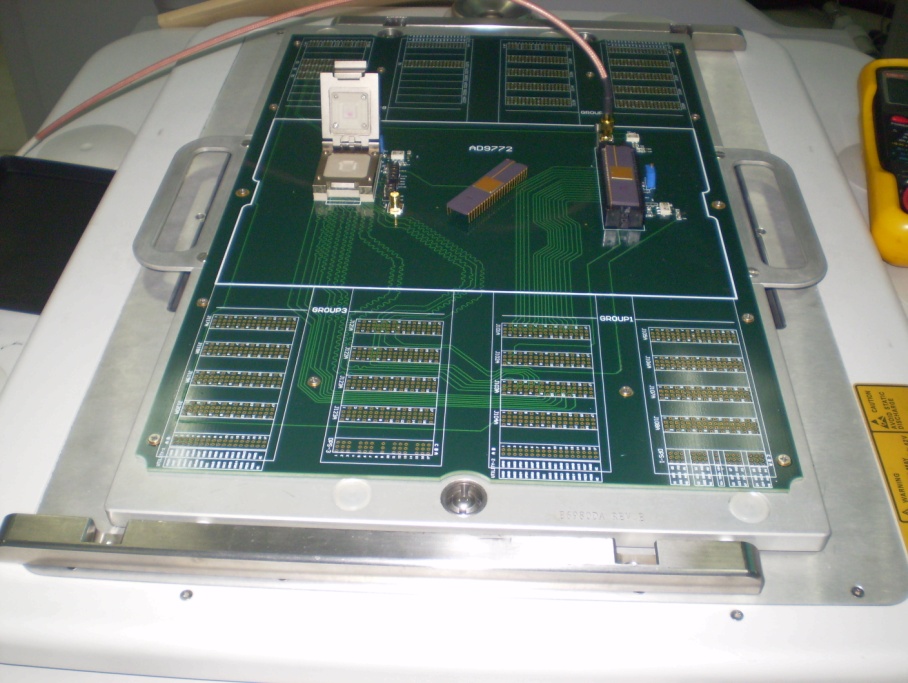

14位D/A动态参数测试版

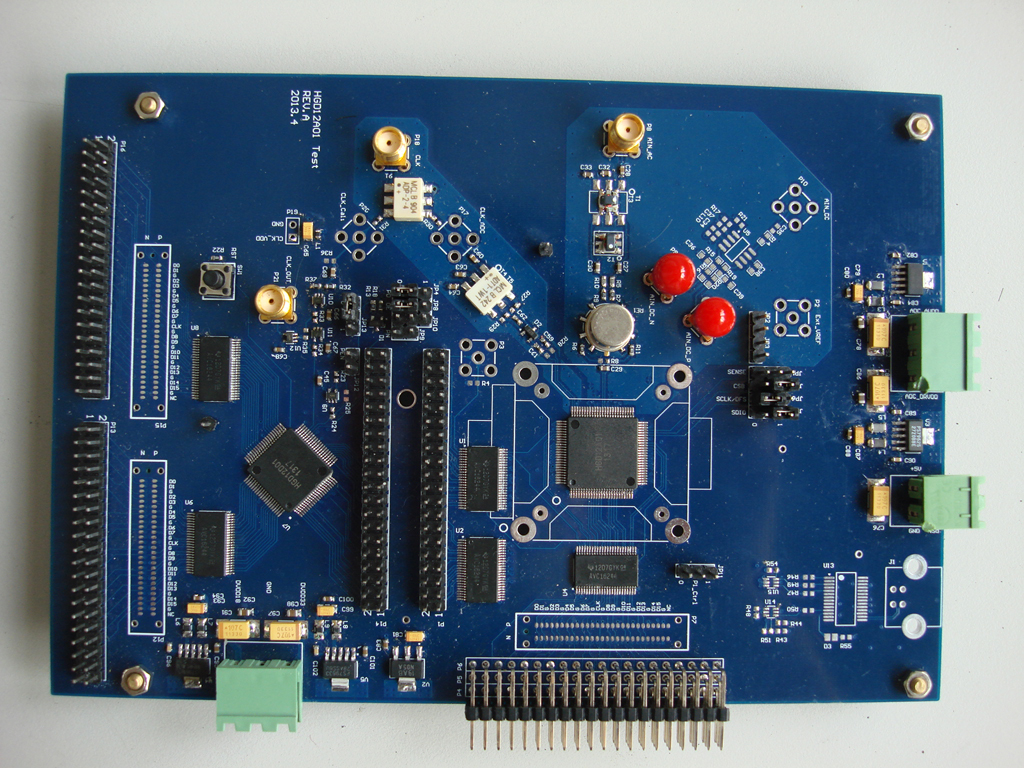

ALTERA开发板

样片测试板